Quỳnh Như Lv 10.000

Senior Member

Intel 4 Process Node In Detail: 2x Density Scaling, 20% Improved Performance

Thông số vật lý của Intel 4: Mật độ bán dẫn cao gấp đôi so với Intel 7, vẫn tiếp tục sử dụng Cobalt.

Tất nhiên, đầu tiên và quan trọng nhất là mật độ. Intel đang cố gắng duy trì Định luật Moore, dù cho việc tăng gấp đôi số lượng bóng bán dẫn trên mỗi thế hệ không còn là vấn đề đơn giản nữa, Intel 4 với mật độ bóng bán dẫn cao hơn sẽ cung cấp các chip nhỏ hơn, hoặc đưa vào nhiều nhânhơn (hoặc phần cứng xử lý khác) với các thiết kế mới hơn.

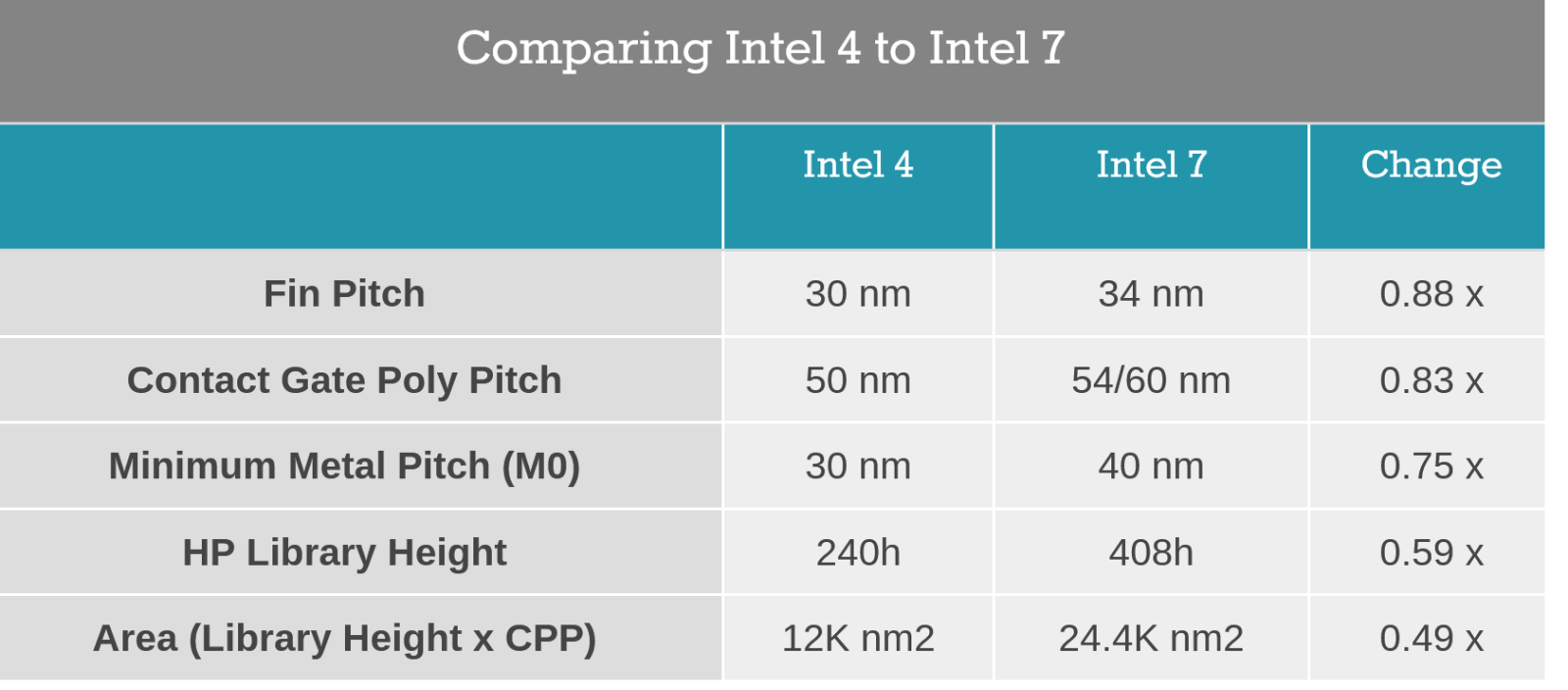

Trong số các số liệu mà Intel công bố, Fin Pitch trên Intel 4 giảm xuống còn 30nm, bằng 0,88 lần kích thước của Fin Pitch 34nm của Intel 7. Tương tự, khoảng cách giữa các cổng tiếp xúc hiện là 50nm, giảm so với 60nm trước đây. Nhưng đáng kể nhất, bước kim loại tối thiểu cho lớp thấp nhất (M0) cũng là 30nm, bằng 0,75 lần kích thước của bước M0 trên Intel 7. Chiều cao thư viện của Intel cũng bị cắt giảm. Chiều cao ô cho thư viện hiệu suất cao(HP) trên Intel 4 là 240nm, chỉ bằng 0,59 lần so với chiều cao của ô HP trên Intel 7.

Kết quả là, Intel tuyên bố tăng gấp 2 lần mật độ cho Intel 4 so với Intel 7, hay cụ thể hơn là giảm một nửa kích thước cho bóng bán dẫn – một cải tiến truyền thống về mật độ bóng bán dẫn của node đầy đủ.

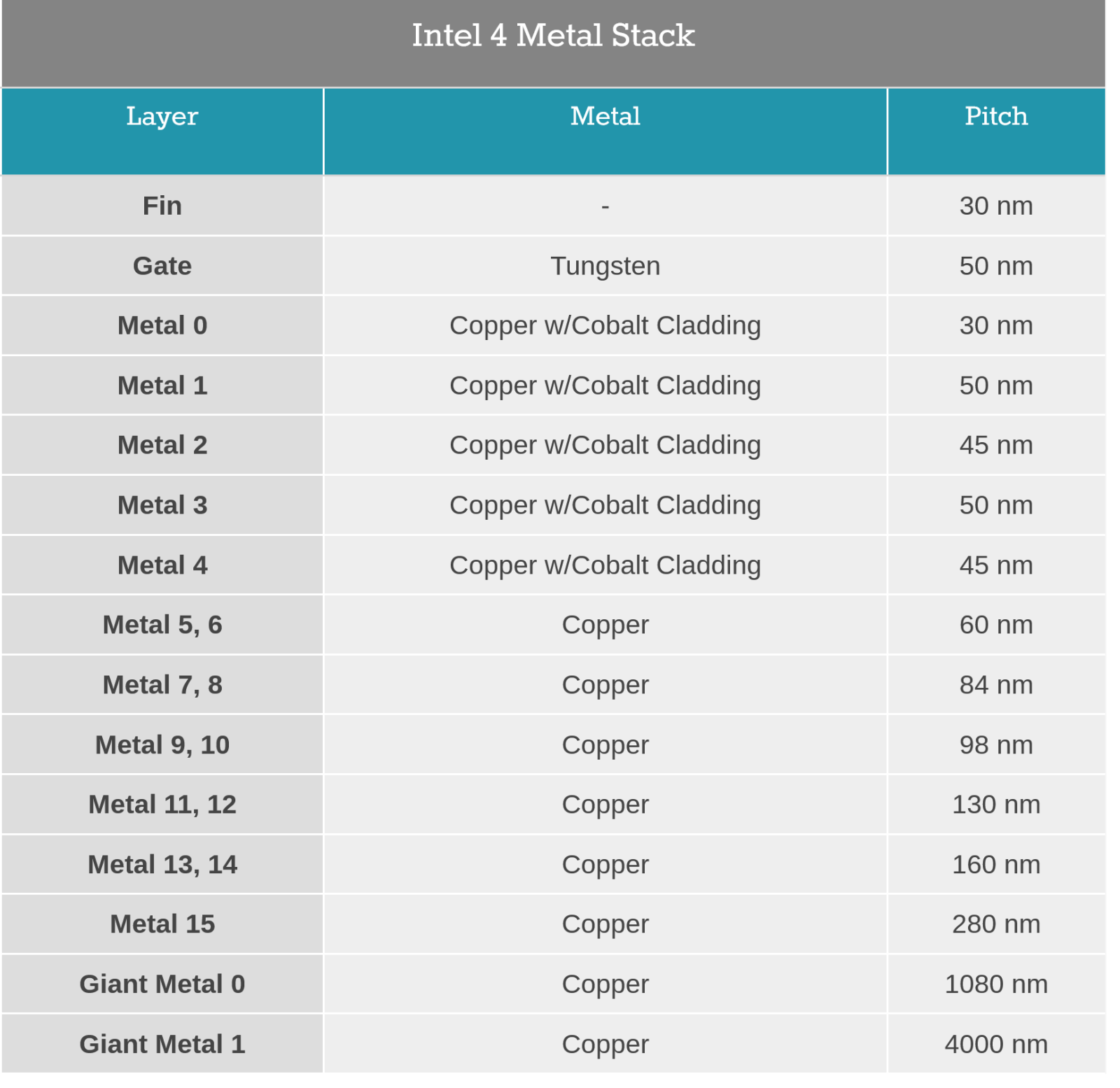

Quay trở lại với quy trình Intel 4, đây là node mới đi kèm với một sự thay đổi lớn ở các lớp kim loại so với các quy trình 10nm trước đây của Intel.

Trong quy trình 10nm của mình, Intel đã thay thế đồng bằng cobalt ở các lớp thấp nhất , điều mà công ty cho là cần thiết vì lý do kéo dài tuổi thọ của bóng bán dẫn(kháng điện di*). Không may là, cobalt không tốt ở góc độ hiệu suất (tốc độ xung nhịp) và từ lâu người ta đã nghi ngờ việc sử dụng cobalt là một trong những trở ngại lớn trong quá trình phát triển node 10nm của Intel.

Ngược lại, đối với Intel 4, Intel đang lùi lại nửa bước. Công ty vẫn đang sử dụng coban trong các quy trình của họ, nhưng thay vì dùng cobanlt nguyên chất, họ đang sử dụng cái mà họ gọi là Đồng tăng cường (eCu) - là đồng được phủ coban. Ý tưởng đằng sau eCu là kết hợp 2 thứ tốt nhất lại thành 1, duy trì hiệu suất của lớp kim loại hóa đồng pha tạp, trong khi vẫn nhận được các lợi ích về khả năng kháng điện di của cobalt.

*Electromigration(điện di) là sự vận chuyển vật chất gây ra bởi sự chuyển động dần dần của các ion trong một dây dẫn do sự truyền động lượng giữa các electron dẫn và các nguyên tử kim loại khuếch tán. Khi kích thước cấu trúc bán dẫn giảm, hiệu ứng này sẽ tăng lên.

Tuổi thọ điện di và Điện trở đường dây được so sánh cho các tùy chọn kim loại khác nhau.

Tuổi thọ điện di và Điện trở đường dây được so sánh cho các tùy chọn kim loại khác nhau.

Số lượng lớp kim loại của Intel 4 đã tăng lên so với Intel 7. Trong khi Intel 7 có 15 lớp kim loại cho logic, thì Intel 4 ép thêm lớp thứ 16. Điều này được kết hợp bởi hai lớp thông thường để định tuyến nguồn, mà Intel gọi là các lớp Giant Metal do các bước tương đối lớn của chúng là 1080nm và 4000nm.

Bên cạnh đó với Intel 4, Intel đã chuyển sang cái mà họ gọi là thiết kế kết nối dạng lưới, thiết kế này chỉ cho phép đặt các via đi giữa các lớp kim loại trên một lưới được xác định trước. Trước đây, via có thể được đặt ở bất cứ đâu, điều này cho phép một số tính linh hoạt nhưngphải đánh đổi vài thứ khác.

Design rules changed from traditional (left) to gridded (right) to improve yield and improve performance though capacitance reduction

Design rules changed from traditional (left) to gridded (right) to improve yield and improve performance though capacitance reduction

Tuần rồi diễn ra Hội nghị chuyên đề VLSI hàng năm của IEEE - một trong những sự kiện lớn của ngành để tiết lộ và thảo luận về các kỹ thuật sản xuất chip mới. Trong số những bài thuyết trình được mong đợi nhất trong năm nay là của Intel - người có mặt tại triển lãm để phác thảo các đặc tính vật lý và hiệu suất của quy trình Intel 4 sắp tới của họ, sẽ được sử dụng cho các sản phẩm dự kiến ra mắt vào năm 2023.

Sự phát triển của Intel Quy trình 4 đại diện cho một cột mốc quan trọng đối với Intel, vì đây là quy trình đầu tiên của Intel kết hợp EUV, và là quy trình đầu tiên vượt qua node 10nm đang gặp khó khăn của họ, đây cũng là cơ hội đầu tiên để Intel giành lại ưu thế về fab.

Quy trình Intel 4 là quy trình 7nm trước đây của Intel, nhưng quy trình Intel 4 là quy trình đầu tiên Intel sử dụng kỹ thuật in EUV cho chip của họ.

Trong một thời gian dài sắp tới, việc sử dụng EUV hứa hẹn cho phép Intel thu nhỏ các đặc tính cần thiết cho các node sản xuất tiên tiến hơn, đồng thời cho phép Intel cắt giảm số bước sản xuất cần thiết thông qua các kỹ thuật DUV đa khuôn mẫu ngày nay.

Điều lạ là Intel là hãng cuối cùng trong số ba nhà sản xuất lớn tham gia vào EUV, intel đã bỏ qua kỹ thuật EUV cho quy trình 10nm vì họ cảm thấy nó chưa sẵn sàng, và sau đó tiếp tục trì hoãn kỹ thuật EUV với quy trình 7nm. Do đó, Intel sẽ tiến lên phía trước dựa trên các thế mạnh do kỹ thuật EUV mang lại, mặc dù họ sẽ phải bù đắp cho thời gian đã mất và lợi thế về kinh nghiệm của TSMC.

Sự phát triển của Intel 4 cuối cùng đã cho phép intel vượt qua quy trình 10nm đang gặp khó khăn của mình. Dù Intel đã cố gắng cải tiến các quy trình 10nm của họ, gần đây nhất là Biến thể 10nm Super Fin nâng cao - mà chúng ta đến với tên gọi intel 7.

Intel tin rằng họ đã cố gắng làm quá nhiều việc cùng một lúc với quy trình 10nm – cả về quy mô và kỹ thuật sản xuất mới, điều này khiến họ phải lùi lại nhiều năm khi gỡ rối mớ hỗn độn đó để tìm và sửa lại những gì đã xảy ra.

Do đó, không có gì ngạc nhiên khi Intel tỏ ra ít tích cực hơn một chút với node EUV đầu tiên của mình, và về tổng thể intel thực hiện cách tiếp cận phát triển theo hướng mô-đun nhiều hơn trong tương lai, cho phép triển khai các công nghệ mới (và nếu cần, gỡ lỗi) theo từng bước.

Sự phát triển của Intel Quy trình 4 đại diện cho một cột mốc quan trọng đối với Intel, vì đây là quy trình đầu tiên của Intel kết hợp EUV, và là quy trình đầu tiên vượt qua node 10nm đang gặp khó khăn của họ, đây cũng là cơ hội đầu tiên để Intel giành lại ưu thế về fab.

Quy trình Intel 4 là quy trình 7nm trước đây của Intel, nhưng quy trình Intel 4 là quy trình đầu tiên Intel sử dụng kỹ thuật in EUV cho chip của họ.

Trong một thời gian dài sắp tới, việc sử dụng EUV hứa hẹn cho phép Intel thu nhỏ các đặc tính cần thiết cho các node sản xuất tiên tiến hơn, đồng thời cho phép Intel cắt giảm số bước sản xuất cần thiết thông qua các kỹ thuật DUV đa khuôn mẫu ngày nay.

Điều lạ là Intel là hãng cuối cùng trong số ba nhà sản xuất lớn tham gia vào EUV, intel đã bỏ qua kỹ thuật EUV cho quy trình 10nm vì họ cảm thấy nó chưa sẵn sàng, và sau đó tiếp tục trì hoãn kỹ thuật EUV với quy trình 7nm. Do đó, Intel sẽ tiến lên phía trước dựa trên các thế mạnh do kỹ thuật EUV mang lại, mặc dù họ sẽ phải bù đắp cho thời gian đã mất và lợi thế về kinh nghiệm của TSMC.

Sự phát triển của Intel 4 cuối cùng đã cho phép intel vượt qua quy trình 10nm đang gặp khó khăn của mình. Dù Intel đã cố gắng cải tiến các quy trình 10nm của họ, gần đây nhất là Biến thể 10nm Super Fin nâng cao - mà chúng ta đến với tên gọi intel 7.

Intel tin rằng họ đã cố gắng làm quá nhiều việc cùng một lúc với quy trình 10nm – cả về quy mô và kỹ thuật sản xuất mới, điều này khiến họ phải lùi lại nhiều năm khi gỡ rối mớ hỗn độn đó để tìm và sửa lại những gì đã xảy ra.

Do đó, không có gì ngạc nhiên khi Intel tỏ ra ít tích cực hơn một chút với node EUV đầu tiên của mình, và về tổng thể intel thực hiện cách tiếp cận phát triển theo hướng mô-đun nhiều hơn trong tương lai, cho phép triển khai các công nghệ mới (và nếu cần, gỡ lỗi) theo từng bước.

Trước tiên quy trình Intel 4 sẽ được sử dụng cho SoC client Meteor Lake sắp ra mắt của Intel, dự kiến sẽ là nền tảng của bộ xử lý Core thế hệ thứ 14.

Mặc dù vẫn chưa thể giao giao hàng cho đến năm 2023, Intel đã thiết lập và chạy Meteor Lake trong phòng thí nghiệm của họ. Cùng với việc mang lại một cú hích đáng kể trong công nghệ xử lý, Meteor Lake cũng sẽ là CPU máy khách đầu tiên sử dụng thiết kế chiplet.

Mặc dù vẫn chưa thể giao giao hàng cho đến năm 2023, Intel đã thiết lập và chạy Meteor Lake trong phòng thí nghiệm của họ. Cùng với việc mang lại một cú hích đáng kể trong công nghệ xử lý, Meteor Lake cũng sẽ là CPU máy khách đầu tiên sử dụng thiết kế chiplet.

Thông số vật lý của Intel 4: Mật độ bán dẫn cao gấp đôi so với Intel 7, vẫn tiếp tục sử dụng Cobalt.

Tất nhiên, đầu tiên và quan trọng nhất là mật độ. Intel đang cố gắng duy trì Định luật Moore, dù cho việc tăng gấp đôi số lượng bóng bán dẫn trên mỗi thế hệ không còn là vấn đề đơn giản nữa, Intel 4 với mật độ bóng bán dẫn cao hơn sẽ cung cấp các chip nhỏ hơn, hoặc đưa vào nhiều nhânhơn (hoặc phần cứng xử lý khác) với các thiết kế mới hơn.

Trong số các số liệu mà Intel công bố, Fin Pitch trên Intel 4 giảm xuống còn 30nm, bằng 0,88 lần kích thước của Fin Pitch 34nm của Intel 7. Tương tự, khoảng cách giữa các cổng tiếp xúc hiện là 50nm, giảm so với 60nm trước đây. Nhưng đáng kể nhất, bước kim loại tối thiểu cho lớp thấp nhất (M0) cũng là 30nm, bằng 0,75 lần kích thước của bước M0 trên Intel 7. Chiều cao thư viện của Intel cũng bị cắt giảm. Chiều cao ô cho thư viện hiệu suất cao(HP) trên Intel 4 là 240nm, chỉ bằng 0,59 lần so với chiều cao của ô HP trên Intel 7.

Kết quả là, Intel tuyên bố tăng gấp 2 lần mật độ cho Intel 4 so với Intel 7, hay cụ thể hơn là giảm một nửa kích thước cho bóng bán dẫn – một cải tiến truyền thống về mật độ bóng bán dẫn của node đầy đủ.

Vì cấu trúc của chip là dạng 2D, số liệu mà Intel sử dụng là nhân chiều cao của ô HP với cao độ poly được tiếp xúc, cơ bản là chiều rộng của ô.

Kết quả là diện tích của ô trên Intel 4 là 12.000nm², bằng 0.49 lần so với intel 7 (24.408nm²).

Tất nhiên, không phải mọi loại cấu trúc đều có quy mô giống nhau với một node quy trình mới và Intel 4 cũng không là ngoại lệ. Các ô SRAM trên Intel 4 chỉ có kích thước bằng khoảng 0.77 lần so với các ô tương tự trên Intel 7. Vì vậy, trong khi các ô logic được tiêu chuẩn hóa đã tăng gấp đôi về mật độ, thì mật độ SRAM (đối với các loại SRAM tương đương) chỉ được cải thiện khoảng 30% hoặc hơn .

Không may là trong khi Intel đang nói về mật độ đối với các cell tiêu chuẩn, họ không chính thức tiết lộ số liệu về mật độ bóng bán dẫn thực tế. Hiện tại, những gì Intel đang nói với chúng tôi là mật độ bóng bán dẫn tổng thể tương ứng tốt với con số gấp 2 lần mà họ hiện đang cung cấp. Dựa trên những gì chúng ta biết về Intel 7 có mật độ 80 triệu bóng bán dẫn trên mỗi mm² cho các thư viện HP, thì các thư viện HP của Intel 4 sẽ có khoảng 160 triệu bán dẫn/mm².

Vì những số liệu này dành cho các thư viện hiệu năng cao có mật độ thấp hơn của Intel, nên câu hỏi là những số liệu dành cho các thư viện mật độ cao sẽ như thế nào? Theo truyền thống, mọi thứ thậm chí còn bị siết chặt hơn để đổi lấy tốc độ xung nhịp giảm. Hóa ra, Intel sẽ không phát triển các thư viện mật độ cao cho Intel 4. Thay vào đó, Intel 4 sẽ là một node hiệu suất cao thuần túy và các thiết kế mật độ cao sẽ đi kèm với node kế tiếp - Intel 3.

Intel đã áp dụng một chiến lược tick-tock để phát triển node trong nửa thập kỷ tới hoặc lâu hơn nữa, node ban đầu dựa trên công nghệ mới (VD máy EUV hoặc máy High-NA), sau đó tiếp tục phát triển thêm/tối ưu hóa. Trong trường hợp của Intel 4, mặc dù nó đang thực hiện công việc tiên phong quan trọng đối với EUV trong các nhà máy của Intel, nhưng các kế hoạch lớn hơn của công ty là để Intel 3 trở thành node EUV tồn tại lâu dài.

Tóm lại, Intel không cần thư viện mật độ cao với Intel 4, vì nó dự kiến sẽ được thay thế bằng Intel 3 với đầy đủ tính năng hơn trong vòng một năm hoặc lâu hơn. Và vì Intel 3 có thiết kế tương thích với Intel 4, rõ ràng là Intel đang thúc đẩy các nhóm thiết kế của riêng mình sử dụng quy trình intel 3 bất cứ khi nào thời gian biểu cho phép. Các khách hàng của Intel Foundry Services cũng sẽ gặp tình huống tương tự – họ có thể sử dụng Intel 4, nhưng IFS tập trung hơn vào việc cung cấp quyền truy cập và trợ giúp thiết kế với Intel 3.

Kết quả là diện tích của ô trên Intel 4 là 12.000nm², bằng 0.49 lần so với intel 7 (24.408nm²).

Tất nhiên, không phải mọi loại cấu trúc đều có quy mô giống nhau với một node quy trình mới và Intel 4 cũng không là ngoại lệ. Các ô SRAM trên Intel 4 chỉ có kích thước bằng khoảng 0.77 lần so với các ô tương tự trên Intel 7. Vì vậy, trong khi các ô logic được tiêu chuẩn hóa đã tăng gấp đôi về mật độ, thì mật độ SRAM (đối với các loại SRAM tương đương) chỉ được cải thiện khoảng 30% hoặc hơn .

Không may là trong khi Intel đang nói về mật độ đối với các cell tiêu chuẩn, họ không chính thức tiết lộ số liệu về mật độ bóng bán dẫn thực tế. Hiện tại, những gì Intel đang nói với chúng tôi là mật độ bóng bán dẫn tổng thể tương ứng tốt với con số gấp 2 lần mà họ hiện đang cung cấp. Dựa trên những gì chúng ta biết về Intel 7 có mật độ 80 triệu bóng bán dẫn trên mỗi mm² cho các thư viện HP, thì các thư viện HP của Intel 4 sẽ có khoảng 160 triệu bán dẫn/mm².

Vì những số liệu này dành cho các thư viện hiệu năng cao có mật độ thấp hơn của Intel, nên câu hỏi là những số liệu dành cho các thư viện mật độ cao sẽ như thế nào? Theo truyền thống, mọi thứ thậm chí còn bị siết chặt hơn để đổi lấy tốc độ xung nhịp giảm. Hóa ra, Intel sẽ không phát triển các thư viện mật độ cao cho Intel 4. Thay vào đó, Intel 4 sẽ là một node hiệu suất cao thuần túy và các thiết kế mật độ cao sẽ đi kèm với node kế tiếp - Intel 3.

Intel đã áp dụng một chiến lược tick-tock để phát triển node trong nửa thập kỷ tới hoặc lâu hơn nữa, node ban đầu dựa trên công nghệ mới (VD máy EUV hoặc máy High-NA), sau đó tiếp tục phát triển thêm/tối ưu hóa. Trong trường hợp của Intel 4, mặc dù nó đang thực hiện công việc tiên phong quan trọng đối với EUV trong các nhà máy của Intel, nhưng các kế hoạch lớn hơn của công ty là để Intel 3 trở thành node EUV tồn tại lâu dài.

Tóm lại, Intel không cần thư viện mật độ cao với Intel 4, vì nó dự kiến sẽ được thay thế bằng Intel 3 với đầy đủ tính năng hơn trong vòng một năm hoặc lâu hơn. Và vì Intel 3 có thiết kế tương thích với Intel 4, rõ ràng là Intel đang thúc đẩy các nhóm thiết kế của riêng mình sử dụng quy trình intel 3 bất cứ khi nào thời gian biểu cho phép. Các khách hàng của Intel Foundry Services cũng sẽ gặp tình huống tương tự – họ có thể sử dụng Intel 4, nhưng IFS tập trung hơn vào việc cung cấp quyền truy cập và trợ giúp thiết kế với Intel 3.

Quay trở lại với quy trình Intel 4, đây là node mới đi kèm với một sự thay đổi lớn ở các lớp kim loại so với các quy trình 10nm trước đây của Intel.

Trong quy trình 10nm của mình, Intel đã thay thế đồng bằng cobalt ở các lớp thấp nhất , điều mà công ty cho là cần thiết vì lý do kéo dài tuổi thọ của bóng bán dẫn(kháng điện di*). Không may là, cobalt không tốt ở góc độ hiệu suất (tốc độ xung nhịp) và từ lâu người ta đã nghi ngờ việc sử dụng cobalt là một trong những trở ngại lớn trong quá trình phát triển node 10nm của Intel.

Ngược lại, đối với Intel 4, Intel đang lùi lại nửa bước. Công ty vẫn đang sử dụng coban trong các quy trình của họ, nhưng thay vì dùng cobanlt nguyên chất, họ đang sử dụng cái mà họ gọi là Đồng tăng cường (eCu) - là đồng được phủ coban. Ý tưởng đằng sau eCu là kết hợp 2 thứ tốt nhất lại thành 1, duy trì hiệu suất của lớp kim loại hóa đồng pha tạp, trong khi vẫn nhận được các lợi ích về khả năng kháng điện di của cobalt.

*Electromigration(điện di) là sự vận chuyển vật chất gây ra bởi sự chuyển động dần dần của các ion trong một dây dẫn do sự truyền động lượng giữa các electron dẫn và các nguyên tử kim loại khuếch tán. Khi kích thước cấu trúc bán dẫn giảm, hiệu ứng này sẽ tăng lên.

Mặc dù Intel không còn sử dụng cobalt nguyên chất, nhưng ở một số khía cạnh, về tổng thể việc sử dụng cobalt của họ đang tăng lên. Trong khi các quy trình 10nm của Intel chỉ sử dụng cobalt cho cổng tiếp xúc và hai lớp kim loại đầu tiên, thì Intel 4 đang mở rộng việc sử dụng eCu cho 5 lớp kim loại đầu tiên.

Tuy nhiên, Intel đã loại bỏ cobalt khỏi cổng, giờ họ đang sử dụng vonfram nguyên chất, chứ không phải là hỗn hợp của vonfram và cobalt.

Tuy nhiên, Intel đã loại bỏ cobalt khỏi cổng, giờ họ đang sử dụng vonfram nguyên chất, chứ không phải là hỗn hợp của vonfram và cobalt.

Số lượng lớp kim loại của Intel 4 đã tăng lên so với Intel 7. Trong khi Intel 7 có 15 lớp kim loại cho logic, thì Intel 4 ép thêm lớp thứ 16. Điều này được kết hợp bởi hai lớp thông thường để định tuyến nguồn, mà Intel gọi là các lớp Giant Metal do các bước tương đối lớn của chúng là 1080nm và 4000nm.

Bên cạnh đó với Intel 4, Intel đã chuyển sang cái mà họ gọi là thiết kế kết nối dạng lưới, thiết kế này chỉ cho phép đặt các via đi giữa các lớp kim loại trên một lưới được xác định trước. Trước đây, via có thể được đặt ở bất cứ đâu, điều này cho phép một số tính linh hoạt nhưngphải đánh đổi vài thứ khác.

Theo Intel, việc sử dụng lưới đã cải thiện cả năng suất của quy trình bằng cách giảm tính biến thiên, cũng như cách họ tiến hành tối ưu hóa các thiết kế. Công tắc cũng có một lợi ích phụ là cho phép Intel tránh phải sử dụng các tổ hợp EUV đa khuôn mẫu cho các kết nối của chúng.

Việc sử dụng EUV cũng cho phép Intel giảm số bước (và số lượng Mask) cần thiết để chế tạo chip. Mặc dù công ty không đưa ra con số tuyệt đối, nhưng trên cơ sở tương đối, Intel 4 yêu cầu số lượng Mask ít hơn 20% so với Intel 7. Nếu Intel không làm điều này, số lượng Mask cần thiết sẽ tăng lên khoảng 30% do số lượng các bước đa khuôn mẫu yêu cầu.

Việc sử dụng EUV cũng cho phép Intel giảm số bước (và số lượng Mask) cần thiết để chế tạo chip. Mặc dù công ty không đưa ra con số tuyệt đối, nhưng trên cơ sở tương đối, Intel 4 yêu cầu số lượng Mask ít hơn 20% so với Intel 7. Nếu Intel không làm điều này, số lượng Mask cần thiết sẽ tăng lên khoảng 30% do số lượng các bước đa khuôn mẫu yêu cầu.

Việc sử dụng EUV cũng có tác động tích cực đến sản lượng của Intel. Mặc dù công ty không cung cấp con số chính xác, nhưng việc giảm số lượng các bước mang sẽ giảm sai sót có thể gây ra lỗi trên tấm wafer.

Hiệu suất của Intel 4: Hiệu suất cao hơn 21,5% ở công suất đồng nhất, giảm 40% năng lượng ở tần số đồng nhất.

Intel đang chứng kiến mức tăng trên trung bình về cả tần số và hiệu quả sử dụng năng lượng.

Hiệu suất của Intel 4: Hiệu suất cao hơn 21,5% ở công suất đồng nhất, giảm 40% năng lượng ở tần số đồng nhất.

Intel đang chứng kiến mức tăng trên trung bình về cả tần số và hiệu quả sử dụng năng lượng.

Ở mức công suất đồng nhất 0,65v, tốc độ xung nhịp có thể đạt được tăng 21,5% so với Intel 7. Như đã nói, 0,65v nằm ở cuối đường cong và biểu đồ của Intel cho thấy lợi nhuận giảm dần khi bạn tiến xa hơn trong điện áp; ở mức 0,85v và hơn thế nữa, mức tăng công suất đồng đều là gần 10%. Theo Intel, họ có thể tiết kiệm thêm 5% hoặc hơn bằng cách sử dụng các ô được thiết kế cho điện áp ngưỡng cao hơn (8VT), dẫn đến chi phí tổng mức tiêu thụ điện năng cao hơn so với các ô tiêu chuẩn.

Intel đang báo cáo mức tăng thậm chí còn lớn hơn về mặt hiệu suất năng lượng với Intel 4. Ở tần số đồng nhất (trong trường hợp này là khoảng 2,1 GHz) Intel đang thấy mức tiêu thụ điện năng thấp hơn 40%. Một lần nữa, lợi nhuận giảm dần khi tần số tăng (cho đến khi Intel 7 đạt đến giới hạn thực tế), nhưng nó nhất quán hơn so với mức tăng hiệu suất/tần số. Điều này phản ánh những gì chúng ta đã thấy với các node xử lý khác(bao gồm cả Intel 7 khi ra mắt) trong đó các node mới hơn đang giảm mức tiêu thụ điện năng ở tốc độ lớn hơn nhiều so với tốc độ chúng cho phép tốc độ xung nhịp cao hơn. Một CPU đầy đủ được xây dựng trên quy trình Intel 4 có thể tiết kiệm được rất nhiều năng lượng – miễn là bạn không phiền khi nó có xung nhịp thấp hơn trước đây.

Mức tăng hiệu suất được nêu trong giấy của Intel phản ánh những gì họ đã tuyên bố cho đến nay, chẳng hạn như mức tăng 20% hiệu suất trên mỗi watt cho Intel 4 được thảo luận tại bản cập nhật lộ trình quy trình vào mùa hè năm ngoái.

Trong năm ngoái, Intel đã tiến gần đến vạch đích để phát triển Intel 4, vì vậy như bài báo của họ phác thảo, họ dường như đang đi đúng hướng để mang lại hiệu suất mong muốn.

Trong khi đó, Intel cũng đang báo cáo những bước phát triển tốt về quy mô chi phí từ Intel 7 lên Intel 4, mặc dù một lần nữa công ty không cung cấp con số cụ thể.

Suy cho cùng thì 1 lớp EUV vẫn đắt hơn 1 lớp DUV, nhưng vì EUV loại bỏ một loạt các mô hình đa khuôn mẫu nên giúp giảm tổng chi phí bằng cách giảm tổng số bước. Việc chuyển sang EUV cũng giúp giảm một chút áp lực vốn đối với Intel, vì Intel 4 không yêu cầu nhiều không gian phòng sạch..

Cuối cùng, khi Intel có kế hoạch xuất xưởng Meteor Lake và các sản phẩm Intel 4 thế hệ đầu tiên khác vào năm 2023, điều còn lại cần xem là Intel có thể thiết lập node quy trình mới của họ nhanh như thế nào và sản xuất số lượng lớn ra sao.

Với các mẫu của Meteor Lake đã có trong phòng thí nghiệm của Intel, Intel đang ngày càng tiến gần hơn đến việc bước vào thời đại EUV. Nhưng đối với Intel để đạt được điều đó có nghĩa là không chỉ tăng quy mô sản xuất từ nhà máy phát triển Hillsboro, mà còn làm chủ được nhiệm vụ là sao chép quy trình đó sang Ireland và các nhà máy khác của Intel sẽ được sử dụng cho Intel 4.

Intel đang báo cáo mức tăng thậm chí còn lớn hơn về mặt hiệu suất năng lượng với Intel 4. Ở tần số đồng nhất (trong trường hợp này là khoảng 2,1 GHz) Intel đang thấy mức tiêu thụ điện năng thấp hơn 40%. Một lần nữa, lợi nhuận giảm dần khi tần số tăng (cho đến khi Intel 7 đạt đến giới hạn thực tế), nhưng nó nhất quán hơn so với mức tăng hiệu suất/tần số. Điều này phản ánh những gì chúng ta đã thấy với các node xử lý khác(bao gồm cả Intel 7 khi ra mắt) trong đó các node mới hơn đang giảm mức tiêu thụ điện năng ở tốc độ lớn hơn nhiều so với tốc độ chúng cho phép tốc độ xung nhịp cao hơn. Một CPU đầy đủ được xây dựng trên quy trình Intel 4 có thể tiết kiệm được rất nhiều năng lượng – miễn là bạn không phiền khi nó có xung nhịp thấp hơn trước đây.

Mức tăng hiệu suất được nêu trong giấy của Intel phản ánh những gì họ đã tuyên bố cho đến nay, chẳng hạn như mức tăng 20% hiệu suất trên mỗi watt cho Intel 4 được thảo luận tại bản cập nhật lộ trình quy trình vào mùa hè năm ngoái.

Trong năm ngoái, Intel đã tiến gần đến vạch đích để phát triển Intel 4, vì vậy như bài báo của họ phác thảo, họ dường như đang đi đúng hướng để mang lại hiệu suất mong muốn.

Trong khi đó, Intel cũng đang báo cáo những bước phát triển tốt về quy mô chi phí từ Intel 7 lên Intel 4, mặc dù một lần nữa công ty không cung cấp con số cụ thể.

Suy cho cùng thì 1 lớp EUV vẫn đắt hơn 1 lớp DUV, nhưng vì EUV loại bỏ một loạt các mô hình đa khuôn mẫu nên giúp giảm tổng chi phí bằng cách giảm tổng số bước. Việc chuyển sang EUV cũng giúp giảm một chút áp lực vốn đối với Intel, vì Intel 4 không yêu cầu nhiều không gian phòng sạch..

Cuối cùng, khi Intel có kế hoạch xuất xưởng Meteor Lake và các sản phẩm Intel 4 thế hệ đầu tiên khác vào năm 2023, điều còn lại cần xem là Intel có thể thiết lập node quy trình mới của họ nhanh như thế nào và sản xuất số lượng lớn ra sao.

Với các mẫu của Meteor Lake đã có trong phòng thí nghiệm của Intel, Intel đang ngày càng tiến gần hơn đến việc bước vào thời đại EUV. Nhưng đối với Intel để đạt được điều đó có nghĩa là không chỉ tăng quy mô sản xuất từ nhà máy phát triển Hillsboro, mà còn làm chủ được nhiệm vụ là sao chép quy trình đó sang Ireland và các nhà máy khác của Intel sẽ được sử dụng cho Intel 4.

như thời thằng máy ủi AMD chả nhét 1 rổ trans vào mà vẫn yếu và nóng hơn Sandy của tèo

như thời thằng máy ủi AMD chả nhét 1 rổ trans vào mà vẫn yếu và nóng hơn Sandy của tèo

tôi chỉ quan tâm hiệu năng/giá thành

tôi chỉ quan tâm hiệu năng/giá thành